Master's Thesis

# A PRODUCT-LINE-BASED APPROACH FOR CONSTRUCTING SYNTHETIC SOFTWARE-ANALYSIS BENCHMARKS

GERD ALLIU

July 07, 2023

## Advisors:

Florian Sattler Chair of Software Engineering

Kallistos Weis Chair of Software Engineering

## Examiners:

Prof. Dr. Sven Apel

Chair of Software Engineering

Prof. Dr. Jan Reineke Real-Time and Embedded Systems Lab

Chair of Software Engineering Saarland Informatics Campus Saarland University

Gerd Alliu: A Product-Line-based Approach for Constructing Synthetic Software-Analysis Benchmarks, © July 2023

## Erklärung

Ich erkläre hiermit, dass ich die vorliegende Arbeit selbständig verfasst und keine anderen als die angegebenen Quellen und Hilfsmittel verwendet habe.

## Statement

I hereby confirm that I have written this thesis on my own and that I have not used any other media or materials than the ones referred to in this thesis

## Einverständniserklärung

Ich bin damit einverstanden, dass meine (bestandene) Arbeit in beiden Versionen in die Bibliothek der Informatik aufgenommen und damit veröffentlicht wird.

## **Declaration of Consent**

I agree to make both versions of my thesis (with a passing grade) accessible to the public by having them added to the library of the Computer Science Department.

Saarbrücken,\_

(Datum/Date)

(Unterschrift/Signature)

### ABSTRACT

Many modern software systems have large numbers of configuration options, which enables them to meet many requirements in a flexible manner. However, the large number of configurations that can be enacted from such options presents a challenge in terms of the analysis of software systems, considering how each or most of a given system's configurations have to be profiled and analyzed for the analysis to be meaningful. To that end, analysis methods have been developed which adequately deal with the complexity that high amounts of configurability introduce, though their development is considerably difficult. In fact, during their development researchers can face significant practical challenges. These challenges can arise due to the lack of access to configurable software systems with adequately documented configurations and certain properties of interest, which would help researchers validate and improve their methods. Moreover, researchers do not have adequate tools that allow them to simulate behaviors of interest in such systems, thus preventing them from being able to address edge cases during their work. Based on these insights, we propose a Product-Line-based approach for producing synthetic benchmarks that match researchers' needs. Crucially, we make use of microarchitectural ideas to ensure that the behaviors of such benchmarks are meaningful and transparent. Overall, we envision that our work will prove valuable to researchers in their quest for better analysis methods, and ignite more interest in using configurability for building benchmarks.

## CONTENTS

| 1 | Introduction |         |                                                         |    |

|---|--------------|---------|---------------------------------------------------------|----|

|   | 1.1          | Conte   | xt                                                      | 1  |

|   | 1.2          | Motiva  | ation                                                   | 2  |

|   | 1.3          | Solutio | on                                                      | 3  |

|   | 1.4          | Overv   | iew                                                     | 5  |

| 2 | Back         | kground | ł                                                       | 7  |

|   | 2.1          | Config  | gurable Software Systems                                | 7  |

|   |              | 2.1.1   | Configurability & Feature-Oriented Software Development | 7  |

|   |              | 2.1.2   | Software Product Lines                                  | 9  |

|   | 2.2          | Comp    | uter Architecture                                       | 11 |

|   |              | 2.2.1   | Basic Notions                                           | 11 |

|   |              | 2.2.2   | Memory                                                  | 12 |

|   |              | 2.2.3   | Pipelined Processing                                    | 14 |

|   | 2.3          | Perfor  | mance Monitoring                                        | 16 |

|   |              | 2.3.1   | Metrics and Tooling                                     | 16 |

|   |              | 2.3.2   | Important Metrics                                       | 17 |

|   | 2.4          | Synthe  | etic Benchmarks                                         | 18 |

| 3 | Арр          | roach   |                                                         | 19 |

|   | 3.1          | Overv   | iew                                                     | 19 |

|   | 3.2          | Forma   | lization                                                | 26 |

|   | -            | 3.2.1   | The Gadget                                              | 26 |

|   |              | 3.2.2   | Impact Mappings                                         | 29 |

|   |              | 3.2.3   | Ground Truth                                            | 32 |

|   |              | 3.2.4   | Benchmarks                                              | 34 |

| 4 | Imp          | lementa | ation                                                   | 37 |

| • | 4.1          | Frame   | -                                                       | 37 |

|   | 4.2          | Gadge   | ets                                                     | 40 |

|   |              | 4.2.1   | Derivation                                              | 40 |

|   |              | 4.2.2   | The Cache Gadget                                        | 41 |

|   |              | 4.2.3   | The Branch Prediction Gadget                            | 46 |

|   | 4.3          | Config  | gurable System Templates                                | 50 |

|   | 4.4          | Limita  | tions and Details                                       | 51 |

| 5 | Eval         | uation  |                                                         | 53 |

|   | 5.1          | Resear  | rch Questions                                           | 53 |

|   |              | 5.1.1   | Research Question 1                                     | 53 |

|   |              | 5.1.2   | Research Question 2                                     | 54 |

|   | 5.2          | Opera   | tionalization                                           | 55 |

|   |              | 5.2.1   | Research Question 1                                     | 57 |

|   |              | 5.2.2   | Research Question 2                                     | 58 |

|   | 5.3          | Result  | s                                                       | 59 |

|   |              | 5.3.1   | Research Question 1                                     | 60 |

|   |            | 5.3.2 Research Question 2           | 65 |

|---|------------|-------------------------------------|----|

|   | 5.4        | Discussion                          | 68 |

|   |            | 5.4.1 Research Question 1           | 68 |

|   |            | 5.4.2 Research Question 2           | 70 |

|   | 5.5        | Threats to Validity                 | 72 |

| 6 | Rela       | ited Work                           | 75 |

|   | 6.1        | Computer Architecture               | 75 |

|   | 6.2        | Configurable Software Systems       | 75 |

|   | 6.3        | Benchmarks and Fault Injection      | 76 |

| 7 | Conclusion |                                     |    |

|   | 7.1        | Future Work                         | 77 |

|   |            | 7.1.1 Potential Improvements        | 77 |

|   |            | 7.1.2 New Avenues                   | 78 |

|   | 7.2        | Summary                             | 78 |

| Α | App        | pendix                              | 81 |

|   | A.1        | Template Feature-Models             | 81 |

|   |            | A.1.1 The <i>Scrambler</i> template | 81 |

|   |            | A.1.2 The <i>Memo</i> template      | 81 |

|   | A.2        | Reproducibility Results             | 81 |

|   | Bibl       | iography                            | 89 |

89

## LIST OF FIGURES

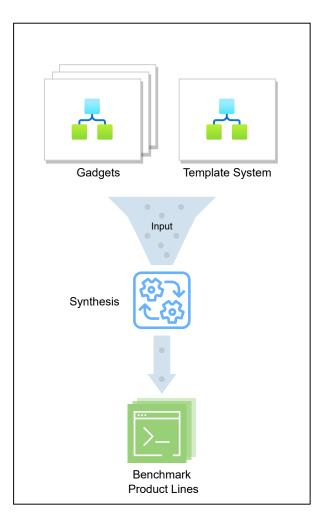

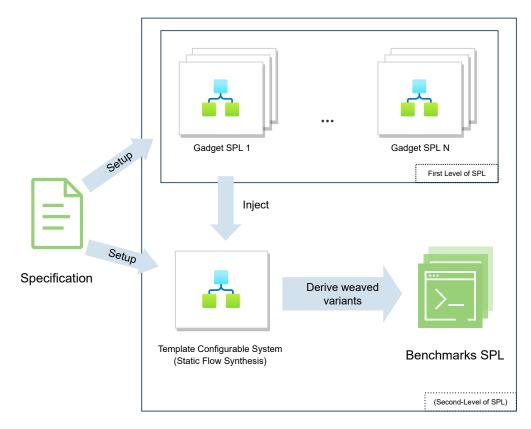

| Figure 1.1 | A high-level, configurability-based solution concept. Gadgets and a template system are funneled into a synthesis process through which we can produce families of synthetic benchmarks.                                                                                                                                                                        | 4  |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

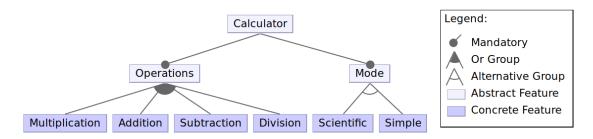

| Figure 2.1 | Feature Model for a simple Calculator. Stemming from a feature<br>with children features, OR groups indicate that at least one of the<br>child features must be selected, whereas Alternative (XOR) groups<br>indicate that at least and at most one child feature must be selected.<br>A mandatory feature is one that must be selected if and only if its     | 4  |

|            | parent is selected. The root feature is always selected                                                                                                                                                                                                                                                                                                         | 8  |

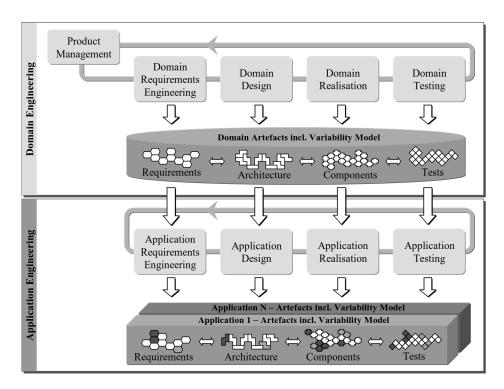

| Figure 2.2 | Software Product Line (SPL) processes, adapted from [17]                                                                                                                                                                                                                                                                                                        | 10 |

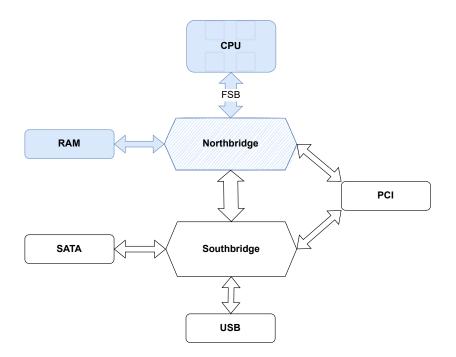

| Figure 2.3 | Internal organization of a computer system. The parts related to the                                                                                                                                                                                                                                                                                            |    |

|            | Northbridge are highlighted in blue                                                                                                                                                                                                                                                                                                                             | 11 |

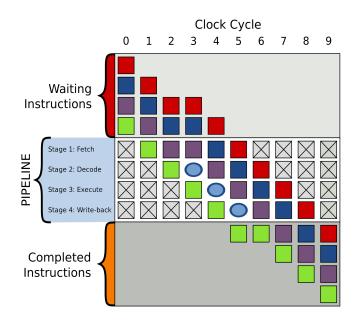

| Figure 2.4 | Pipeline Bubbles, shown in blue ellipses. Adapted from Wikipedia <sup>1</sup> .                                                                                                                                                                                                                                                                                 | 15 |

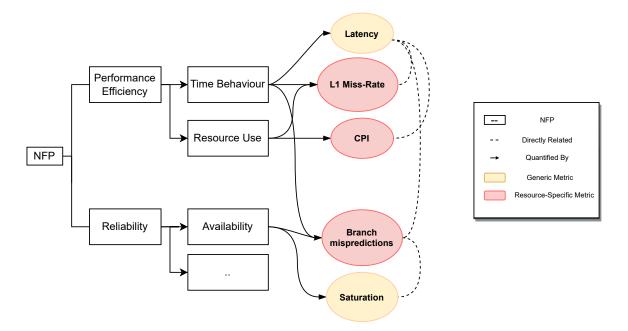

| Figure 3.1 | Non-Functional Properties (NFPs) and types of metrics. NFPs are bro-                                                                                                                                                                                                                                                                                            |    |

|            | ken down into sub-attributes. The sub-attributes are then quantified                                                                                                                                                                                                                                                                                            |    |

|            | using generic or resource-specific metrics (cf. Chapter 2)                                                                                                                                                                                                                                                                                                      | 20 |

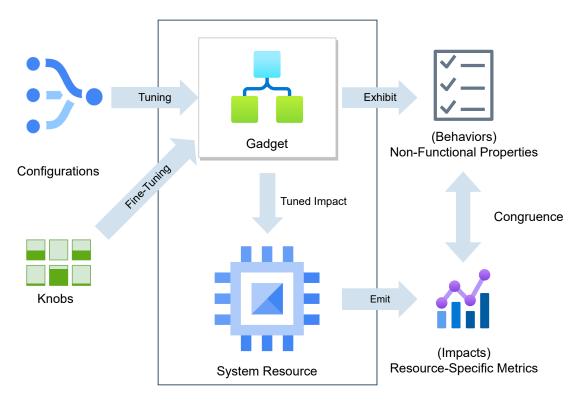

| Figure 3.2 | The Gadget Concept.                                                                                                                                                                                                                                                                                                                                             | 22 |

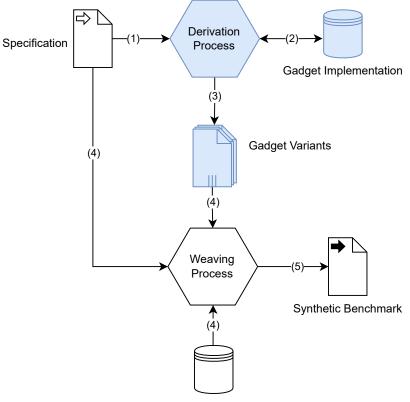

| Figure 3.3 | Synthesis Concept. Parts pertaining to the gadget SPLs are highlighted                                                                                                                                                                                                                                                                                          |    |

| <b>F</b> ' | in blue.                                                                                                                                                                                                                                                                                                                                                        | 24 |

| Figure 3.4 | Two-Level SPL concept in full display.                                                                                                                                                                                                                                                                                                                          | 25 |

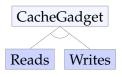

| Figure 3.5 | Simplified feature-model for the Cache Gadget. The model allows for either Reads or Writes to be enabled                                                                                                                                                                                                                                                        | 28 |

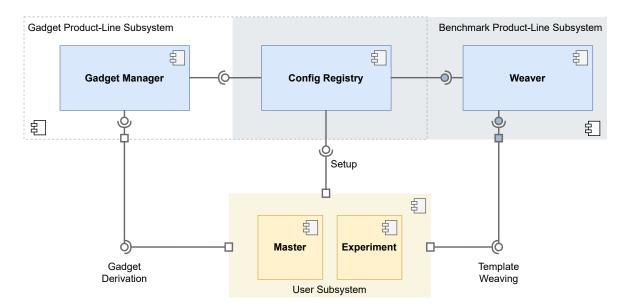

| Figure 4.1 | Component view of the framework, in UML 2.0 notation [44]. The                                                                                                                                                                                                                                                                                                  | 20 |

| Figure 4.1 | shaded gray area depicts the subsystem related to the "weaving"                                                                                                                                                                                                                                                                                                 |    |

|            | process. The area encircled by a dashed line depicts the subsystem                                                                                                                                                                                                                                                                                              |    |

|            | related to the gadget SPLs and the corresponding derivation process.                                                                                                                                                                                                                                                                                            |    |

|            | The area in yellow depicts the user-facing components. Interfaces                                                                                                                                                                                                                                                                                               |    |

|            | are shown using the "lollipop" notation whereby the component                                                                                                                                                                                                                                                                                                   |    |

|            | connected to the circle provides the interface, and the component                                                                                                                                                                                                                                                                                               |    |

|            | connected to the sickle implements that interface. At the level of                                                                                                                                                                                                                                                                                              |    |

|            | subsystems, interfaces are unified, shown as small rectangles (ports)                                                                                                                                                                                                                                                                                           |    |

|            | on the edge of each subsystem.                                                                                                                                                                                                                                                                                                                                  | 38 |

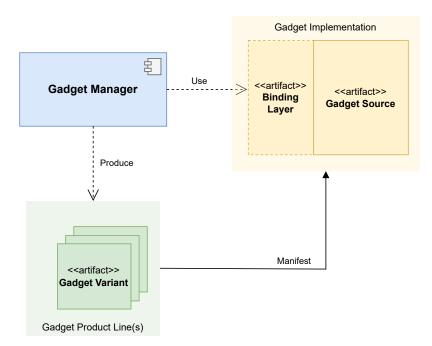

| Figure 4.2 | Depiction of the Gadget Manager's interaction with the gadget imple-<br>mentation. Notably, the gadget implementation provides a binding<br>layer as an interface to the Gadget Manager, through which important<br>decisions regarding feature-selections and subsequent in-code bind-<br>ings are handled. The actual implementation of features is contained | 30 |

|            | in the source artifact.                                                                                                                                                                                                                                                                                                                                         | 41 |

### X LIST OF FIGURES

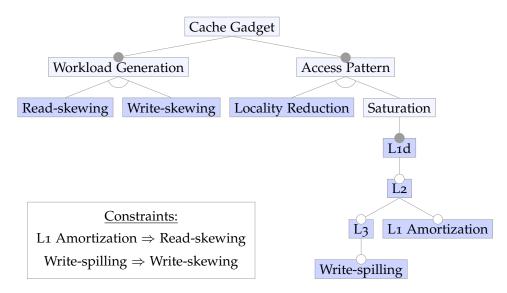

| Figure 4.3               | Complete feature-model for the Cache Gadget. The indicated con-<br>straints can be read as logical implications, e.g. the selection of                                                                                                                                                                                                                                                                                                                                       |          |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

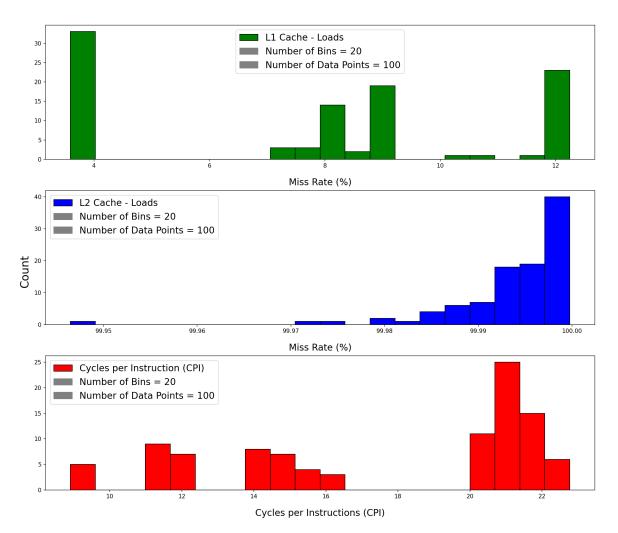

| Figure 4.4               | Write-spilling implies the selection of Write-skewing A histogram of frequency distributions for samples of values of L1 Load Miss-Rate, L2 Load Miss-Rate and CPI. The number of bins used was set to 20 as it better captured the overall pattern of the distribution. The measurements were performed in a reference architecture, which we introduce during evaluation Chapter 5                                                                                         | 42<br>44 |

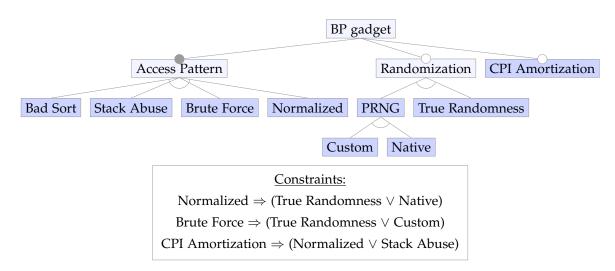

| Figure 4.5               | Complete feature-model for the Branch Prediction Gadget. Con-<br>straints should be read as logical implications.                                                                                                                                                                                                                                                                                                                                                            | 44       |

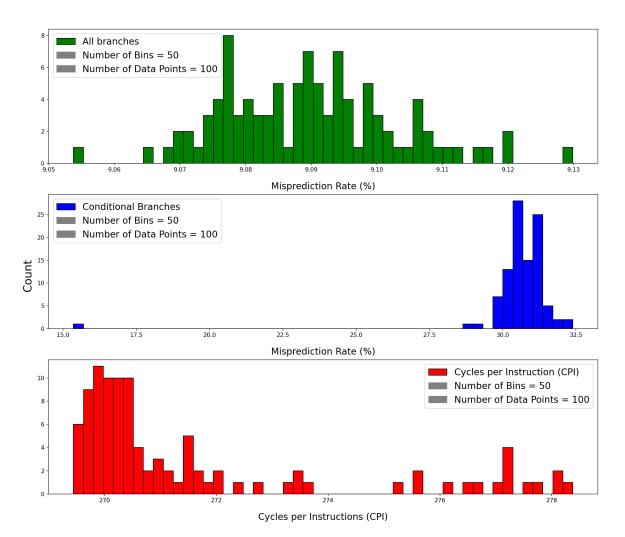

| Figure 4.6               | A histogram of frequency distributions for samples of values of<br>Branch Misprediction Rate, Conditional Branch Misprediction Rate<br>and CPI is shown. The number of bins used was set to the large value<br>of 50, since lower values smoothen the overall shape significantly.<br>The measurements were performed in a reference architecture, which                                                                                                                     |          |

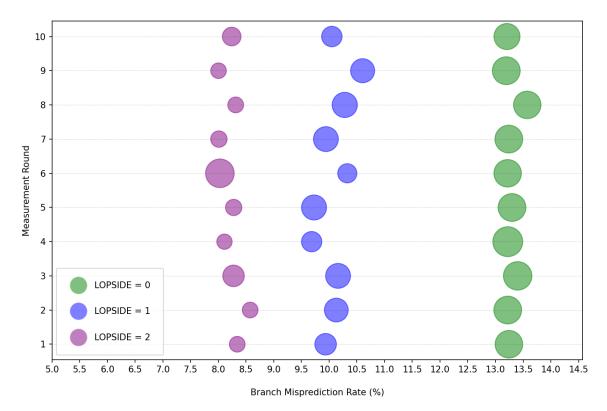

| Figure 4.7               | we introduce during the evaluation in Chapter 5 A bubble plot indicating the effect of the Lopside knob. We perform 10 rounds of measurements. In each round, we take a measurement for each of the three knob values. The measurement rounds are shown in the y-axis. The size of each bubble (data point) indicates the value of the CPI obtained in the same round, relative to the other bubbles. The observed behavior is consistent with the description in Table 4.4. | 48       |

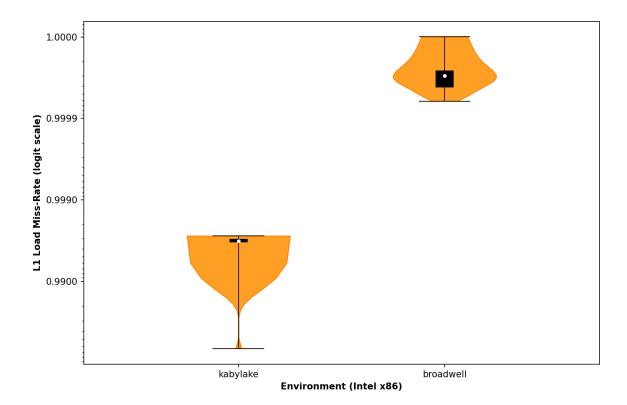

| Figure 5.1               | Violin plots, with embedded box-plots, for two of the four Intel<br>environments. The violins are constructed using Kernel-Density Esti-<br>mation (KDE), with a density parameter of 20. The white-dot in each<br>box-plot indicates the median. Each violin corresponds to a sample<br>of values of L1 Load Miss-Rate for $v_1$ of the Cache Gadget                                                                                                                        | 50<br>70 |

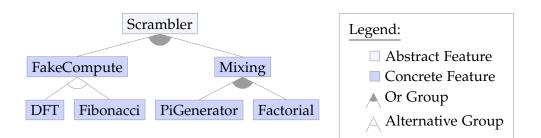

| Figure A.1               | Complete feature-model for the Scrambler template. DFT and Fibonacci provide series of computations, in tandem with the scrambling that is generated from the Mixing elements. For instance, Fibonacci uses a recursive implementation that generates the corresponding series, and uses the elements in the series to generate the numbers of $\pi$ using a Taylor series formula. Alternatively, a Factorial can be taken for each element in the Fibonacci series.        | 81       |

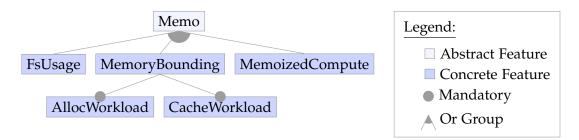

| Figure A.2               | Complete feature-model for the Memo template. FsUsage indicates<br>a functionality that performs file operations. Memoized Compute<br>refers to a memoized implementation of a simple computation task.<br>AllocWorkload and CacheWorkload perform close-to-optimal mem-<br>ory allocations and cache accesses.                                                                                                                                                              | 81       |

| Figure A.3               | Mean values for the gadget variants, in the Kabylake environment.                                                                                                                                                                                                                                                                                                                                                                                                            | 82       |

| Figure A.4               | Mean values for the gadget variants, in the Haswell environment                                                                                                                                                                                                                                                                                                                                                                                                              | 83       |

| Figure A.5               | Mean values for the gadget variants, in the Broadwell environment.                                                                                                                                                                                                                                                                                                                                                                                                           | 84       |

| Figure A.6<br>Figure A.7 | CoV values for the gadget variants, in the Kabylake environment<br>CoV values for the gadget variants, in the Haswell environment                                                                                                                                                                                                                                                                                                                                            | 85<br>86 |

~

## LIST OF TABLES

| Table 2.1 | Example NFPs and their types, based on [39]                                              | 17 |

|-----------|------------------------------------------------------------------------------------------|----|

| Table 3.1 | Examples of resource-specific metrics, calculated on the basis of                        |    |

|           | specific counters. See Chapter 4 for complete lists of such metrics.                     | 21 |

| Table 4.1 | Metrics used to quantify the behavior of the Cache Gadget.                               | 43 |

| Table 4.2 | Knobs used in the Cache Gadget for fine-tuning of impacts                                | 45 |

| Table 4.3 | Metrics used to quantify the behavior of the Branch Prediction Gadget.                   | 47 |

| Table 4.4 | Knobs used in the Branch Prediction Gadget for fine-tuning of impacts.                   | 49 |

| Table 5.1 | Gadget variants and the corresponding feature-selections. The feature-                   |    |

|           | models for each gadget were introduced in Chapter 4                                      | 56 |

| Table 5.2 | Subject systems used as test environments for our measurements and                       |    |

|           | experiments. The green-shaded row denotes the reference environ-                         |    |

|           | ment. Note that the L1d and L2 caches sizes are shown as individual                      |    |

|           | (per-core) sizes. The overall L1d and L2 capacities can be found by                      |    |

|           | multiplying the given values with the number of cores                                    | 57 |

| Table 5.3 | Descriptive statistics ( $\mu$ , CoV) for the Reference Impact-Mapping                   |    |

|           | (IM <sub>ref</sub> ) of the Cache Gadget. The green-shaded cells indicate targeted       |    |

|           | metrics, whereas the red-shaded cells indicate potential side-effects.                   |    |

|           | Values are rounded to two decimal points.                                                | 61 |

| Table 5.4 | Bootstrapped 90% Confidence-Intervals for the $IM_{ref}$ of the Cache                    |    |

|           | Gadget. Values are rounded to at least two decimal points, and to                        |    |

|           | as many decimal points as needed to make the interval boundaries                         |    |

|           | noticeable                                                                               | 61 |

| Table 5.5 | Descriptive statistics ( $\mu$ , CoV) for the IM <sub>ref</sub> of the Branch Prediction |    |

|           | Gadget. The green-shaded cells indicate targeted metrics, whereas                        |    |

|           | the red-shaded cells indicate potential side-effects.Values are rounded                  |    |

|           | to two decimal points.                                                                   | 62 |

| Table 5.6 | Bootstrapped 90% Confidence-Intervals for the $IM_{ref}$ of the Branch                   |    |

|           | Prediction Gadget. Values are rounded to at least two decimal points,                    |    |

|           | and to as many decimal points as needed to make the interval bound-                      |    |

|           | aries noticeable.                                                                        | 62 |

| Table 5.7 | Results for the normality tests regarding the $IM_{ref}$ and other Impact-               |    |

|           | Mappings (IMs) of the Cache Gadget, shown for each of four test                          |    |

|           | environments: S=Skylake, K=Kabylake, H=Haswell, B=Broadwell.                             |    |

|           | Each checkmark indicates that the corresponding sample is likely                         |    |

|           | obtained from a normally-distributed population                                          | 63 |

| Table 5.8  | Results for the normality tests regarding the IM <sub>ref</sub> and other IMs of the Branch Prediction Gadget, shown for each of four test environments: S=Skylake, K=Kabylake, H=Haswell, B=Broadwell. Each checkmark indicates that the corresponding sample is likely obtained from a normally-distributed population.                                                                                                                                                                                                                                                                                                                                                                                                               | 63 |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Table 5.9  | Results of the Kruskal-Wallis tests regarding the Cache Gadget, ob-<br>tained for the four Intel environments. Green-shaded cells indicate<br>cases when the $H_{k_0}$ would be retained. Yellow-shaded cells indicate<br>cases when the hypothesis is rejected but would be retained if we had<br>used only the Skylake and Kabylake environments in the test. Red-<br>shaded cells indicate cases when a total loss of impact was observed<br>in one of the four environments. NT=Non-Targeted                                                                                                                                                                                                                                        | 64 |

| Table 5.10 | Results of the Kruskal-Wallis tests regarding the Branch Prediction Gadget, obtained for the four Intel environments. Green-shaded cells indicate cases when the $H_{k_0}$ would be retained. Yellow-shaded cells indicate cases when the hypothesis is rejected but would be retained if we had used only the Skylake and Kabylake environments in the test. Red-shaded cells indicate cases when a total loss of impact was observed in one of the four environments. NT=Non-Targeted                                                                                                                                                                                                                                                 | 64 |

| Table 5.11 | Partial results regarding the IM of each gadget, in the AMD Zen3 environment. NA=Not-Available. NT=Non-targeted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 65 |

| Table 5.12 | The breakdown of our one-sample t-tests regarding our experiment with manually defined expected values. # indicates counts, whereas $\delta_{\mu}$ indicates the mean of the differences obtained by subtracting the manually defined expected-value from the mean of each sample for which we perform a test, and then taking the average value of these differences. The $\delta_{\mu}$ is a percentage because the concerned metrics are also percentages (e.g. L2 Miss-Rate).                                                                                                                                                                                                                                                       | 66 |

| Table 5.13 | The results for the ANOVA-based verification regarding cases when pairs provide different effects than their reordered counterparts.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 67 |

| Table 5.14 | Results on several <i>benchmarks</i> , generated on the basis of multiple<br>Injective System-Gadget Mappings (ISGs) that are obtained using<br>uniform random sampling of all gadget variants, and a single variant<br>of a template system. The green-shaded cells indicate cases when<br>the metric is targeted by at least one of the injected gadget variants<br>and the measured impact is significantly higher than the baseline.<br>Yellow-shaded cells indicate cases when the metric is targeted by at<br>least one injected gadget variant but the measured impact is only<br>slightly higher than the baseline. The red-shaded cells indicate non-<br>targeted metrics for which we see a potential side-effect in terms of |    |

|            | the measured impact.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 68 |

## LISTINGS

| Listing 2.1 | Structural Feature Interaction due to control flow. Each feature is enabled on the basis of a preprocessor directive. For instance, if |    |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------|----|

|             | the MULTIPLICATION macro is defined, the code that implements                                                                          |    |

|             | the Multiplication feature will be included during compilation, and                                                                    |    |

|             | therefore in the final executable.                                                                                                     | 9  |

| Listing 4.1 | Sample configuration artifact for the gadget SPLs, where we specify                                                                    |    |

|             | the variant using a named identifier, and an assignment of values to                                                                   |    |

|             | the knobs for each variant. When knob assignments are omitted, a                                                                       |    |

|             | default assignment is used.                                                                                                            | 38 |

| Listing 4.2 | Configuration artifact for the Injection Points. Each Injection Point                                                                  |    |

|             | has a unique numeric ID.                                                                                                               | 39 |

| Listing 4.3 | Injection Points embedded in a template configurable system. Each                                                                      |    |

| 0.10        | injection point includes its unique ID and a fixed suffix. They are                                                                    |    |

|             | replaced during weaving, with function calls that "invoke" specific                                                                    |    |

|             | gadget variants. Weaving will also add the correct header files to link                                                                |    |

|             | the shared libraries that constitute gadget variants.                                                                                  | 39 |

| Listing 5.1 | The feature-interaction example introduced in Chapter 2, but now                                                                       | 57 |

| 2100118 912 | with injection points. Injecting gadget variants at these points will                                                                  |    |

|             | make the feature-interaction have a distinct profile w.r.t. the metrics                                                                |    |

|             | 1                                                                                                                                      |    |

|             | that the injected gadgets target                                                                                                       | 71 |

## ACRONYMS

- BPU Branch Prediction Unit

- BTB Branch Target Buffer

- CPI Cycles per Instruction

- CPU Central Processing Unit

- CoV Coefficient of Variation

- FOSD Feature-Oriented Software Development

- GT Ground Truth

- ILP Instruction-Level Parallelism

- IM Impact-Mapping

- IM<sub>ref</sub> Reference Impact-Mapping

- ISG Injective System-Gadget Mapping

- IS Instruction Set

- LRNG Linear (Congruential) Random Number Generator

- MSR Model-Specific Register

- NFP Non-Functional Property

- PEBS Precise Event-Based Sampling

- PHT Pattern History Table

- PMU Performance-Monitoring Unit

- PRNG Pseudo-Random Number Generator

- RAM Random Access Memory

- RNG Random Number Generator

- SPL Software Product Line

- TLB Translation Lookaside Buffer

#### INTRODUCTION

#### 1.1 CONTEXT

Many modern software systems comprise a large number of configuration options, typically in the hundreds [1]. These options can enable entire pieces of functionality in the system that constitute *features* of that system. As such, software systems can have multiple features, as well as many valid combinations of these features. Moreover, a combination of features constitutes a standalone *configuration* of the system and represents a variant of the system with distinct characteristics. It is also commonplace to have many features interact with one another - that is, the presence of one feature imposes some often unintended changes in the workings of another feature during program execution. We commonly refer to systems that have these characteristics as *configurable software systems*, and the practice of designing software systems by making use of features in a systematic way is known as Feature-Oriented Software Development (FOSD).

For all software systems, the analysis of their non-functional properties (e.g. performance) is important in order to improve their quality. Configurable software systems are no exception to this, though the large number of features and the presence of interactions complicate their analysis in several ways [2–4]. The gist of the issue is that the performance of any such system should be examined by taking into account that different configurations will typically contribute to different performance profiles, due to the inherent changes in functionality enabled by their constituent features. These profiles can be quantified and translated into a *performance model*, which is a mathematical description of the contribution of each feature to the overall performance of a system. To construct such models, one would typically need to profile several configurations and extract the overall contribution of each feature. Based on this, we could then obtain clear expectations about the performance of any other configuration, simply by looking at the presumably known contribution of each of the features it comprises.

That being said, the challenge in constructing such performance models is to not resort to brute-force methods of profiling each and every possible configuration, before determining the performance profile of each individual feature. This is due to the fact that the more configurations are excluded, the less information and hence accuracy we would have in the model, although the process is much less time-consuming. Moreover, the manner in which features interact can obfuscate the performance that each individual feature attains in isolation. As such, the performance profile of a configuration cannot be reliably obtained by simply combining the profiles of the features that participate in that configuration. Typically, this is addressed by detecting, profiling, and including interactions in the performance model itself, alongside features.

Facing issues of complexity and tractability, analysis methods that go well beyond naive (brute-force) ideas have been developed. To that end, many analysis methods can be categorized into either *black-box* or *white-box*. Black-box approaches often rely on learning

#### 2 INTRODUCTION

methods in which the performance profiles of only a subset of the configurations of a program are obtained and then used to derive a performance model that can be used to predict the performance of any other configuration [3]. Moreover, a distinguishing factor of black-box approaches is that the source code of the program is not scrutinized (hence the name). By optimizing the learning process, it is possible to use only a sample of all configurations for the building of a performance model. This way the problem of analysing a huge number of configurations is alleviated. In fact, a big part of the feasibility of many analysis methods rests with the sampling strategy being employed, since it is an effective means of dealing with a huge number of available configurations [3, 5].

Alternatively, white-box approaches can make use of the implementation and structure of a program. Their goal is to automatically scrutinize a program's source code with the aim of extracting clues and important context that helps avoid the sampling of configurations that are redundant with regard to the building of a performance model for the program as a whole. While this adds complexity to the analysis, it can result in better results due to the inclusion of more information. Moreover, it can also better detect and account for feature-interactions [6, 7].

On a similar note, identifying the degree to which configurations are responsible for certain properties, without having complete knowledge of the properties of each configuration, is also possible. For instance, Dubslaff et al. [8] have developed a method for making such explications, using notions of causal inference. Based on that method, they can infer sets of features that are responsible (causes) for certain functional or non-functional properties (effects), as well to determine the degree to which the features in these sets are responsible for said properties.

#### 1.2 MOTIVATION

Based on the analysis techniques described thus far, we observe that it is not always easy or reasonable for researchers to search for and examine existing software systems on the lookout for interesting cases of feature-interactions, large numbers of configurations, or interesting program behaviors. Indeed, the manual labor that is typically involved in scrutinizing existing systems plays a crucial role in specifying a baseline understanding of a system. Moreover, researchers oftentimes need to balance between a deep manual inspection of a few systems, as opposed to a more superficial inspection of a large and varied set of systems.

For instance, Velez et al. [6] relied on several existing systems to determine whether their white-box method was able to correctly detect cases of feature-interactions. The choice of the subject systems played an important role in their work - not only were they real-world examples, they also included a reasonable amount of feature-interactions and certain other characteristics that were deemed to be representative of configurable software systems. Furthermore, the authors had to obtain preliminary knowledge of the actual performance profiles of their subject systems, in order to validate the correctness and efficiency of their method in building performance models.

On a related note, Siegmund et al. [3] constructed a learning-based, black-box method for constructing performance-models, while making intelligent use of sampling notions to make their method tractable. To validate their method, they relied on existing systems

with known configuration options, features, and performance characteristics. However, they correctly noted that the choice of such systems could easily represent a threat to the validity of their approach, mostly due to *overfitting* concerns. Indeed, having a limited number of these systems runs the risk of tailoring the analysis to those systems' characteristics. An analysis tool would rather need to be exposed to different types of systems - that is, systems with varying numbers and types of features and feature-interactions - in order for it to be able to effectively analyze any arbitrary system.

Similarly, Dubslaff et al. [8] also utilized several systems with well-known features and performance models. This knowledge allowed them to determine whether their causalinference method helps in the identification of causes for observed functional or nonfunctional properties. Notably, having a preliminary understanding of the exact behaviors and intricacies of features beforehand enabled them to assess whether their inference method identifies effects and causes correctly. Moreover, this also enabled them to see whether it was possible to assign varying degrees of responsibility and blame to already identified causes, w.r.t their effects.

Overall, these observations have led us to pinpoint the following practical challenges for researchers:

- 1. There is currently no easy way of synthesizing configurable software systems that exhibit specific behaviors (non-functional properties), and have other properties of interest such as feature-interactions.

- Having preliminary knowledge of a configurable software system's feature-wise behavioral profile is currently not possible without prior examination or analysis of said system.

Therefore, our goal in this thesis is to address the aforementioned challenges. We do so by outlining an approach for creating synthetic programs (benchmarks) that exhibit varied, stable and transparent behaviors, on the basis of FOSD and microarchitectural notions. We outline this approach next.

#### 1.3 SOLUTION

To accomplish our goal of enabling researchers to build synthetic programs with desired properties, we rely on notions of configurability and microarchitectures. Microarchitectural considerations directly help us with regard to the synthesis of stable behaviors in our benchmarks. In addition, configurability notions help us facilitate the synthesis of benchmarks with varied behaviors in a structured manner.

Practically speaking, we first construct components with known features and well-defined behaviors, to which we refer as *gadgets*. These components serve as building blocks for the types of benchmarks we intend to create, as they provide us with important traits that enable their modular use in a larger setting. To develop them, we look toward benchmarking literature, focusing specifically on synthetic microbenchmarks [9–12]. These types of benchmarks apply carefully designed workloads to a system with the aim of evaluating specific aspects of that system. In the same spirit, we design our gadgets so that they apply carefully designed workloads onto a system with the aim of simulating scenarios of performance

#### 4 INTRODUCTION

Figure 1.1: A high-level, configurability-based solution concept. Gadgets and a template system are funneled into a synthesis process through which we can produce families of synthetic benchmarks.

regressions, and potentially other behaviors. By design, gadgets offer a small number of features, and therefore a relatively small number of configurations. Importantly, the design of each gadget is such that for each of their configurations we obtain distinct, sizeable, and stable behaviors.

To ensure that our gadgets have stable impacts, we take a resource-focused approach in that we aim to build gadgets that impact specific resources of a system's architecture, such as the Level-3 cache. Firstly, we identify metrics that indicate program behavior from the perspective of an architectural resource. Then, we try to design features that contribute to varied impacts that are noticeable through the chosen metrics. Taking this path enables us to have more control over the behavior of a gadget, which is important for its stability. In addition, focusing on metrics pertaining to low-level resources enables us to quantify and evaluate the behaviors of gadgets effectively. Based on their focused and stable impacts, we make their behavioral profiles transparent to the users.

Nevertheless, gadgets are not the ultimate benchmarks we intend to build. In fact, through the use of gadgets we are able to build synthetic benchmarks with complex behavioral profiles that are of value to researchers. These synthetic benchmarks are crafted in a way that makes use of gadgets' properties in a careful manner. In practice, this requires some degree of automation and application of ideas such as Software Product Lines (SPLs), which refer to families of products that are crafted on the basis of common artifacts as well as configurability. At a high-level, we implement the gadgets in a well-organized manner, and subsequently combine them under existing configurable systems that act as execution templates. This way, we are able to build entire families of benchmarks that can combine the workloads of multiple gadgets in various ways. The specific manner in which this combination is performed constitutes our primary means of producing synthetic benchmarks and is explained in detail in subsequent chapters. A high-level depiction of our solution is provided in Figure 1.1.

Overall, this approach enables us to produce meaningful benchmarks, in the sense that their behaviors are 1) varied, 2) stable, and consequently 3) transparent, stemming from the fact that the gadgets themselves have stable and transparent behaviors by design, and provide a large variety of impacts due to their inherent configurability. Based on these properties, our approach directly addresses the practical challenges we highlighted in the previous section. In fact, having benchmarks with varied behaviors is a direct result of using configurability, and can help researchers in generalizing their analysis methods by testing them using different benchmarks. Similarly, ensuring stable behaviors in these benchmarks makes them reliable in the sense that they can be used when and where the researchers need to subject them to analysis methods. Moreover, stability allows us to document the behaviors and make the intricate workings of our benchmarks accessible to the researchers, which should help them validate their methods more efficiently.

To realize our approach, we implement a framework that provides all the mechanisms needed to create actual benchmarks. Moreover, we evaluate our implementation and the overall approach in detail. Notably, we ensure that the gadgets have stable and transparent behavioral profiles as intended. In addition, we successfully assess their usefulness in building synthetic benchmarks, while also pinpointing potential limitations and improvements. Overall, we believe that our approach adequately addresses the two practical challenges we outlined, and enables researchers to build test systems that directly aid them in improving and developing analysis methods like the ones we described earlier.

#### 1.4 OVERVIEW

To develop our solution in a coherent manner, we structure the rest of the thesis as follows. In Chapter 2, we provide the necessary background needed to read through the thesis while getting a solid understanding of the main ideas. That includes basic notions of software configurability, computer architecture, and performance engineering. In Chapter 3, we provide a detailed description of our approach, and a formal description of the main concepts. In Chapter 4, we then dive into the implementation details and relevant issues, whereas in Chapter 5 we evaluate key aspects of our work. In Chapter 6, we describe the body of literature that inspired and informed many of our ideas. In conclusion, we summarize our contribution and present future-work ideas in Chapter 7.

### BACKGROUND

In this chapter, we present important notions of configurable software systems, computer architecture, performance engineering, and benchmarks. All these concepts help in developing the core ideas of gadgets, their stable and transparent behaviors with regard to architectural resources, and ultimately the synthetic benchmarks that can be built based on our approach.

#### 2.1 CONFIGURABLE SOFTWARE SYSTEMS

In this section, we introduce important notions regarding configurable software systems, which we use throughout the thesis. Notably, we introduce the concepts of Feature-Oriented Software Development (FOSD) and Software Product Line (SPL) in some detail, since these concepts are central to our work.

### 2.1.1 Configurability & Feature-Oriented Software Development

Modern software systems meet numerous and complex requirements through their inherent *variability*. At a high level, variability can be understood as the ability of a software system to change its functional or non-functional properties, so that it fits a specific context [13, 14]. To realize variability, a software system or artifact might comprise several variation points, through which a stakeholder can vary its properties. The end result of variability realization is the obtaining of different *variants* of the same software system [14].

One specific type of variation points are the so-called *configuration options*, which typically refer to explicit parameters in the code artifacts of a software system that can be set by a stakeholder. Notably, configuration options are mostly considered with regard to the functional properties of a system and can facilitate the toggling of entire pieces of functionality. Stemming from this idea, the deliberate and structured use of configuration options gives rise to what is known as *configurability*.

Systematically handling configurability in modern software systems can be challenging, especially during development. While it is possible to try to manage configurability through refactoring and better architectural considerations [1], the proactive approach is to bring configurability to the forefront of the engineering process. This is precisely what FOSD achieves. In FOSD, the focus is on *features* - units of functionality that satisfy a requirement, represent a design decision and provide a potential configuration option [15]. Based on this definition, it is possible to develop software systems in which there is a clear mapping between code fragments and logical functionality, regardless of how the code artifacts are organized from an architectural perspective. In addition, logical functionality can be traced from the early stages of domain analysis and design to that of implementation, since the notion of a feature is explicit in the code artifacts. As such, the FOSD paradigm bridges the observable structure and behavior of a system to its implementation.

Figure 2.1: Feature Model for a simple Calculator. Stemming from a feature with children features, OR groups indicate that at least one of the child features must be selected, whereas Alternative (XOR) groups indicate that at least and at most one child feature must be selected. A mandatory feature is one that must be selected if and only if its parent is selected. The root feature is always selected.

An important notion in FOSD is that of *feature-models* [15, 16]. A common way of modeling the features of a system, as well as their logical organization and constraints is to depict them in a tree diagram, as shown in Figure 2.1. A hierarchical depiction of this kind places the software system at the root, as an abstract feature that represents the overall functional outline of the system. Features are then organized in this hierarchy based on their conceptual meanings, as well as their inter-dependencies and constraints which are usually depicted using notations for logical constructs such as OR, XOR and AND groups. Moving deeper into the tree we may find other abstract features, though we should typically find concrete features at the leaf-nodes. Such a model is easily amenable to propositional logic and reasoning, since it is easy to derive the entire feature-model of a system in propositional form [16].

The features in such models are usually binary, meaning that they can be either enabled or disabled using certain configuration options. For instance, the simple Calculator program shown in Figure 2.1 could include an Addition feature while not including Multiplication. Non-binary features can also be modelled, however we aim to keep the models simple in this work. Considering a model with only binary features, any group of enabled features constitutes a *configuration* of the software system. In addition, if this group of enabled features a *valid configuration*. Moreover, each valid configuration leads to a variant of the system, which is why these terms are often used interchangeably.

Another important concept in FOSD is that of *feature-interactions*. Kolesnikov et al. [2] define a feature-interaction as the case in which the functional or non-functional properties of a feature are influenced by the presence of another feature in the same configuration. A simple case of two interacting features is one in which the corresponding in-code implementations are structurally interrelated in such a way that the implementation of one feature is affected by the presence of the other. However, features might also interact in non-structural ways, especially with regard to non-functional properties.

In Listing 2.1 we show how the implementation of a Multiplication feature can be affected by that of the Scientific feature, based on the model in Figure 2.1. If the latter is enabled, the function that implements the former will receive a different parameter type which may affect its functional logic.

```

#ifdef MULTPLICATION

void config_mul(layout* l, representation r) {...}

#endif

.

.

void setup(layout* l){

r = get_default_representation();

#ifdef MULTIPLICATION

#ifdef SCIENTIFIC

//Interaction

r = get_binary_representation();

#endif

config_mul(l, r);

#endif

.

}

```

Listing 2.1: Structural Feature Interaction due to control flow. Each feature is enabled on the basis of a preprocessor directive. For instance, if the MULTIPLICATION macro is defined, the code that implements the Multiplication feature will be included during compilation, and therefore in the final executable.

#### 2.1.2 Software Product Lines

FOSD provides us with a structured way of handling configurability, from the early stages of domain analysis and design, to the implementation and derivation of different variants. However, in order to further structure the discussion around configurable software systems, we can rely on the notion of a Software Product Line (SPL) [13, 15, 17, 18].

The simplest way of conceptualizing an SPL is to think of all the possible variants that we can derive for a configurable software system, considering its feature-model and configurations. The set of these variants would constitute a *product family*, i.e. a group of different software products that are related to each other in terms of the artifacts they rely on and other commonalities. These artifacts, especially when using FOSD principles, are systematically reused across the entire product family [15, 18]. Besides this notion of systematic reuse, an important idea regarding SPLs is that of decision-making [13, 18]. Naturally, handling an entire set of variants for the same system necessitates decisions such as selecting the desired features to include in a variant, enacting the selection into the code artifacts, and generating (deriving) a final product. The presence of a feature-model greatly helps with the feature selection, though additional tools and methods are usually employed to bind selected features and to perform an automated product derivation.

Overall, the development lifecycle of an SPL is understood in two parts [18], as shown in Figure 2.2. On the top half we depict the Domain Engineering process, in which we conceptualize features and design a feature-model based on overall domain needs (Domain Requirements Engineering & Design), as well as craft code artifacts and introduce configuration options in these artifacts (Domain Realisation & Testing). On the bottom

Figure 2.2: SPL processes, adapted from [17].

half we depict the Application Engineering process in which we make feature selections and architectural decisions regarding the composition of features, guided by specific user requirements (Application Requirements Engineering & Design), and derive actual products (Application Realisation & Testing).

Crucially, the development lifecycle of an SPL is contingent on having a clear approach for the transition from Domain Engineering to Application Engineering. The most important part of this transition is that of being able to translate high-level decisions regarding the functionality that a product of our SPL should have, into low-level decisions that allow us to obtain the actual product. Typically, this transition is facilitated through *binding* decisions. As an example, once we have a feature-selection in mind that would give us a variant of a given configurable software system, we need to translate it into specific decisions with regard to the code artifacts and the configuration options thereof [14], so as to obtain the intended variant (product).

In this work, we rely on development-time binding decisions. Technically speaking, we facilitate bindings through compile-time techniques for handling configurability at the code level. For instance, we rely on *preprocessor directives* like the ones in Listing 2.1 to enact a feature-selection and derive a desired product variant. Looking at the code snippet, we can see that the code corresponding to features that we have not selected will simply be omitted from the compilation, whereas the code that corresponds to selected features is included and contributes to a part of the resulting variant's functionality. This way, all that we would have to do to perform a binding is to use the preprocessor directives correctly.

Figure 2.3: Internal organization of a computer system. The parts related to the Northbridge are highlighted in blue.

#### 2.2 COMPUTER ARCHITECTURE

In order for us to discuss microarchitectural ideas related to our approach, we present key notions regarding memory, caching and branch-prediction. These ideas inform our approach and implementation in subsequent chapters, especially w.r.t. the configurable components we call gadgets.

#### 2.2.1 Basic Notions

For the goals of this thesis, we need to have a common understanding of computer architecture in place. To facilitate the discussion regarding this concept, we present a simplified depiction of a modern computer system's components and their relations in Figure 2.3. The main building blocks shown in the figure are a single Central Processing Unit (CPU), a Random Access Memory (RAM) unit in the role of the main memory, and the main interconnects that can be conceptually organized into the Northbridge and Southbridge [19, 20]. Notably, the Northbridge encompasses all data buses and components that exist between the main memory and the CPU, whereas the Southbridge encompasses all interconnects between the Northbridge and I/O components. An important takeaway from this description is that there exists a large difference in the workings of different components and interconnections; for instance, the rate of data transfers in the Northbridge is much larger than in the Southbridge (hence the distinction).

Furthermore, the CPU usually consists of multiple cores, as well as other components such as caches that are shared among among cores, and which can store both data and

instructions. Each core is tasked with the fetching and processing of instructions, as well as the storing of the results back to memory. Overall, the internal workings of the CPU, as well as its interfacing with the other components, are guided by the *clock frequency* - each CPU works at the pace of a series of pulses that are generated at a (mostly) fixed frequency. Each pulse initiates a computational cycle across all cores, forcing them to make progress in the processing of instructions.

Considering how instructions and data typically reside in memory and need to be fetched before processing, the internal organization of each core comprises three logical parts: 1) the front-end, 2) the back-end (execution engine), and 3) the memory subsystem. The memory subsystem is the primary interface to the Northbridge, and notably contains the Level-2 cache that is shared by the front-end and back-end of the core and which stores both data and instructions. It also includes the Level-1 data-cache for retrieving and storing data from/into memory. Similarly, the front-end contains the Level-1 instructions-cache to handle the fetching of instructions from memory. Lastly, the back-end incorporates all the components that relate to the actual execution of instructions such as register files and arithmetic logic units, and the buffering of the results prior to sending them to the memory subsystem.

#### 2.2.2 Memory

In modern architectures, memory components are organized into conceptual hierarchies relating to their capacities and latencies. As such, we usually see that registers are small yet fast memory units, whereas the caches are progressively larger and slower, and the main memory is the largest and slowest. Practically speaking, accessing data in the main memory can easily take about tens or even hundreds of cycles due to hardware considerations, making for significant processing latencies [19]. The use of multiple levels of caches alleviates this issue, since caches can reduce the number of high-latency accesses to memory, as well as fetch data or instructions from the main memory before they are needed in the CPU [19, 21]. Given this insight, modern computer architectures usually incorporate three<sup>1</sup> levels of caches, typically Levels 1 and 2 which are per core, and Level 3 which is shared among cores. A cache of a higher level is only accessed when the needed data is not found in the cache of the preceding level in what constitutes a *cache miss*, and is typically larger in capacity than its lower level counterparts. For instance, in an Intel Skylake model, the cache sizes for each level can be at most 32, 256 and 2048 Kilobytes, respectively [22]. These are in stark contrast to the sizes of main-memory units which range between 16-256 Gigabytes in most modern systems. Given their limited sizes, caches implement certain policies regarding when and how data need to be inserted, removed and kept.

Since we deal with multi-core CPUs, we usually have several instances of Level-1 and Level-2 caches, whereby each core has a Level-1 and a Level-2 cache. While this is beneficial for performance, cases of inconsistencies between the corresponding per-core caches of the same level could arise when the same memory locations are concerned. For that reason, modern CPUs implement certain algorithms to achieve *cache-coherence*, which refers to the

<sup>1</sup> In many cases there is also a fourth level of caching that stores decoded micro-instructions [22], though this is not of direct relevance to this work.

careful coordination that takes place among cores when performing accesses on caches so as to avoid any inconsistencies [23].

Before diving deeper into caches, it is important to have some notions of memory access in place. The storage pattern of a RAM can be described as a two-dimensional array of cells, each of which can store one bit of data. The typical RAM implementation is *dynamic*, which means that the electric state of each cell needs to be periodically refreshed in order for the data to be preserved. This translates to added waiting delays during memory access. To perform an access, the CPU would need to provide an *address* specifying both row and column indices that identify a cell in the array. However, to avoid inherent hardware delays, common implementations operate at a larger granularity than a single cell whereby multiple rows of cells are read at once. In Intel architectures we usually see memory accesses happening in 8 rapid bursts of 8 bytes, usually amounting to a total of 64 bytes which is also known as a *cache-line* due to the fact that caches typically operate in data chunks of that size [19, 20].

Besides the basic idea of memory accesses, it is important to note that modern CPUs rely on virtual addressing [24]. Virtual addresses present a logical space of memory locations that is much larger than the actual physical one offered by a RAM unit. It is the job of the operating system and the CPU to handle physical-to-virtual address translations. The concerned physical-to-virtual mappings are dynamically maintained in specific memoryresiding data structures called *page-tables*. Importantly, frequent accesses to the page-tables cause significant latencies, which is why these mappings are also cached in the so-called Translation Lookaside Buffers (TLBs). The working principles for TLBs are quite analogous to those of the main caches [19, 25]. Moreover, TLBs are often integrated with the Level-1 and Level-2 caches. Notably, modern Intel systems usually incorporate two levels TLBs, where both levels are per-core and the first level is typically split into separate units for instruction and data, similar to the standard Level-1 caches [22].

Turning our attention back to caching, the main operating principles that underpin caches are *locality*, *prefetching* and *associativity* [20, 26–28]. Locality refers to the usefulness of data or instructions currently residing in a cache for a future computation. Usually, executing instructions tend to relate to a set of data items that reside close to each-other in terms of their locations. Therefore, when an item from this set is used, the other ones will likely be used next and so they need to reside closer to the CPU (spatial locality). Similarly, data items that were recently used tend to be used again in the near future (temporal locality).

Stemming from ideas of locality, modern CPUs make use of hardware logic to predict what data items or instructions will be needed next based on currently cached data, making sure to fetch those items as early as possible so that they can be immediately used when needed. This technique is known as *prefetching* [26, 27]. Both locality and prefetching help ensure that accesses to the main memory are avoided, which is crucial for performance given the high latencies of accessing the main memory. This implies that when an executing process accesses data (or instructions) in ways that do not adhere well to the locality ideas described previously, its performance can deteriorate. An interesting scenario when this can happen is when prefetching is performed for some data items which are expected to be used shortly after, when in fact that data is not used; indeed, this wastes the effort of prefetching and also uses up some of the cache's capacity in a counterproductive way. Overall, bad use of locality and wasteful prefetches lead to significant numbers of misses in the caches [19].

To provide more context, a miss in the Level-2 caches can cause latencies of more than 10 cycles, and those in Level-3 can cause latencies of about 30-60 cycles<sup>2</sup>.

The internal organization of a cache usually tries to balance between having a fixed location for the data residing in each memory address in what is known as *direct-mapped* caching, versus having a free-choice of locations for each address in what is known as associative caching. The former strategy results in faster searching but also in a higher miss-rate since the cache can only contain data for a limited number of addresses, whereas the latter can incur latency due to a large numbers of comparisons during the search for a free location, though it attains lower miss-rates. The common solution is to mix both these ideas, resulting in the so called *set-associative* caching [29]. In set-associative caches, the first bits of an address directly map to a set of locations in the cache, with the correct set being identified through some hashing function that takes these bits as input. The middle bits then index into any locations within that set in a fully associative manner, whereas the last bits serve as offsets for identifying actual blocks of data in a specific location. While this approach is widely used nowadays, it can still have some limitations. One potential issue is that many subsequent accesses to a cache can still map to the same set and exhaust its capacity by using up all of its free locations, similar to what happens in direct-mapped caches, even if there are free locations in other sets. Such occurrences are known as *aliasing* effects [19].

#### 2.2.3 Pipelined Processing

Besides the concept of computer architecture discussed earlier, an important concept is that of an Instruction Set (IS). An IS specifies the types of instructions that a processor can execute, whereas the actual on-chip implementation of an IS is what is commonly referred to as a *microarchitecture*. In this work we consider only x86 microarchitectures, mostly Intel-based implementations due to their common use in practice.

A major challenge in developing a microarchitecture is for the CPU to process as many instructions as possible per cycle. The processing of any instruction is performed in multiple stages. The main stages are 1) Fetching, 2) Decoding, 3) Executing and 4) Write-Back. As such, one major issue is that given the memory hierarchy discussed earlier, stalls may occur when the execution of an instruction requires memory accesses, thus blocking subsequent instructions from starting to execute. Naturally, some parallelism is required in order to process multiple instructions simultaneously instead of stalling an instruction in one of the stages and blocking the overall flow of instructions. The main form of parallelism that modern microarchitectures use is Instruction-Level Parallelism (ILP) [30].

The core idea behind ILP is that the processing of instructions in the aforementioned stages can be overlapped; for instance, while an instruction is in the Decode stage, another instruction can be in the Fetch stage. This way, the processor can make progress on as many instructions as there are stages, implying that the overall processing can obtain an ideal throughput of one instruction per cycle. This way of processing is known as *pipelining*, and a processor that can obtain a theoretical maximum throughput of one instruction per cycle is called a *scalar* processor [30]. Additionally, pipelines in modern systems are further improved by having concurrently executing instructions for some or all of the four stages

<sup>2</sup> Figures are based on reports on Intel's Haswell family of CPUs: https://www.7-cpu.com/cpu/Haswell.html

Figure 2.4: Pipeline Bubbles, shown in blue ellipses. Adapted from Wikipedia<sup>3</sup>.